The method of claim 1, comprising repeating the comparing and the increasing until the capacitance of the first capacitor stage exceeds the sum of the capacitances of the plurality of capacitor stages and of the first capacitor array. In response to the comparing, increasing the capacitance of the first capacitor stage by increasing the capacitance of a second capacitor array when the capacitance of the first capacitor stage is less than the sum of the capacitances of the plurality of capacitor stages and of the first capacitor array, wherein the plurality of capacitor stages, the first capacitor array, and the first capacitor stage are coupled in parallel. comparing a capacitance of a first capacitor stage to a sum of capacitances of a plurality of capacitor stages and of a first capacitor array and.

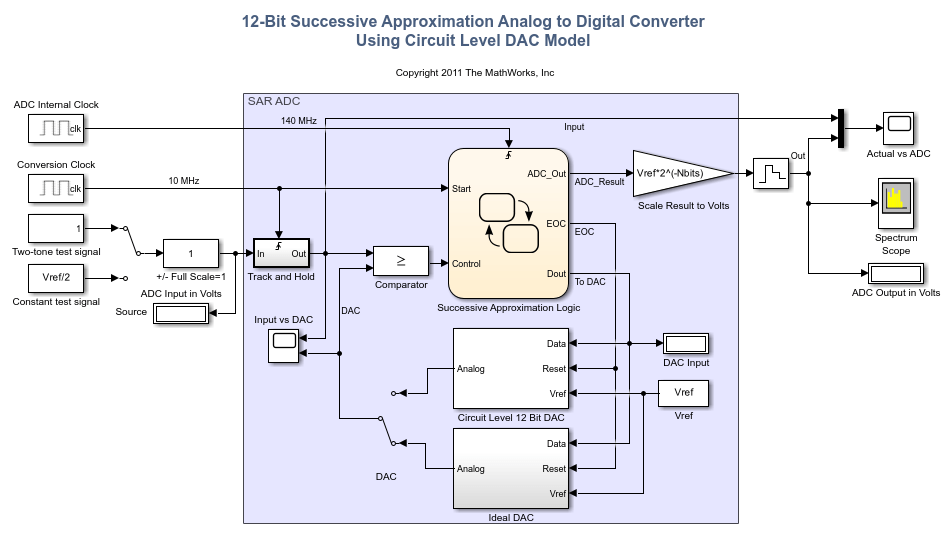

A method of calibrating a successive approximation register (SAR) analog-to-digital converter (ADC), the method comprising:

0 kommentar(er)

0 kommentar(er)